数字IC设计

- 1 min同步电路和异步电路的区别

是否与时钟有固定的因果关系。

什么是亚稳态

亚稳态是指触发器无法在某个规定的时间段内到达一个可以确定的状态。

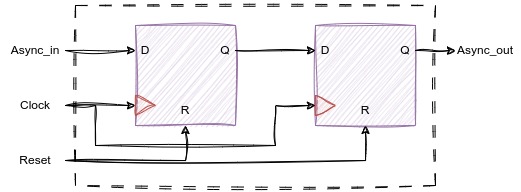

使用两级触发器可以防止亚稳态传播到电路中。

系统最高计算速度

最小时钟周期=触发器输出时间+组合逻辑时延+D触发器建立时间

时钟频率=最小时钟周期的倒数

对于多位的异步信号如何进行同步

- 采用保持寄存器加握手信号的方法

- 异步FIFO

锁存器和触发器的区别

电平敏感的存储器件称为锁存器。

有交叉耦合的们构成的双稳态的存储器件称为触发器。

什么是竞争和冒险现象

在组合电路中,某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称竞争;由于竞争而使电路输出发生瞬时错误的现象叫做冒险。(也就是由于竞争产生的毛刺叫做冒险)。

判断方法:

- 代数法:布尔式中有相反的信号

- 卡诺图:卡诺圈相切

- 实验法:滤波器观察

解决方法:

- 加滤波电容

- 加选通信号

- 增加冗余项消除逻辑冒险

同步复位与异步复位的区别

同步复位在时钟沿发生变化时,完成复位。

异步复位只需要复位信号满足条件就完成复位,要求较高,容易产生毛刺。

摩尔状态机和米利状态机的区别

摩尔状态机:状态输出只跟当前状态有关。

米利状态机:状态输出既和当前状态有关也和当前输入有关。

多时钟域设计中,如何处理信号跨时钟域

进行同步处理。单个信号使用两级触发器来同步;数据或者地址总线跨时钟域可以用异步FIFO;也可以使用握手信号。

SRAM, FLASH, DRAM, SSRAM, SDRAM的区别

- SRAM:静态随机存储器,存储速度快,容量小,掉电数据丢失。常用于缓存。

- FLASH:闪存,存取速度慢,容量大,掉电数据不丢失。

- DRAM:动态随机存储器。必须不断刷新。访问速度快,能耗大,常用作内存。

- SSRAM:同步静态随机存储器,时钟相关。

- SDRAM:同步动态随机存储器,时钟相关。

四种复用方式

- 频分

- 时分

- 码分

- 波分

名词解析

- CMOS:互补金属氧化物半导体

- MCU:微控制单元

- DSP:数字信号处理器

- FPGA:现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

- ASIC:专用集成电路

- PCI:外围组件互联总线标准

集成电路设计流程

-

需求分析。分析用户或市场的需求,并将其翻译成对芯片产品的技术需求。

-

算法设计。设计和优化芯片钟所使用的算法。这一阶段一般使用高级编程语言(如C/C++),利用算法级建模和仿真工具(如MATLAB,SPW)进行浮点和定点的仿真,进而对算法进行评估和优化。

-

构架设计。根据设计的功能需求和算法分析的结果,设计芯片的构架,并对不同的方案进行比较,选择性能价格最优的方案。

-

RTL设计(代码输入)。使用HDL语言完成对设计实体的RTL级描述。

-

RTL验证(功能仿真)。使用仿真工具或其他RTL代码分析工具,验证RTL代码的质量和性能。

-

综合。从RTL代码生成描述实际电路的门级网表文件。

-

门级验证(综合后仿真)。对综合产生的门级网表进行验证。这一阶段通常会使用仿真、静态时序分析和形式验证等工具。

-

布局布线。后端设计对综合产生的门级网表进行布局规划(Floorplanning)、布局(Placement)、布线(Routing),生成生产用的版图。

-

电路参数提取确定芯片中互连线的寄生参数,从而获得门级的延时信息。

-

版图后验证。根据后端设计后取得的新的延时信息,再次验证设计是否能够实现所有的功能和性能指标。

-

芯片生产。生产在特定的芯片工艺线上制造出芯片。

-

芯片测试。对制造好的芯片进行测试,检测生产中产生的缺陷和问题。